前言

当ECU之间使用CAN来进行通信时,总线上发生了什么?我们可以借助示波器来观察总线上的电平,而从示波器上我们可以看到一串连续的高低起伏的“线条”——波形。无论是电磁波或者是总线上变化的电平,这些信息的载波在时间和空间上是连续的。而从这段连续的载波中解读出我们所需要的信息就需要借助一定的采集手段——采样。CAN控制器需要从总线的高低电平中获取到逻辑0和1。那么控制器要在哪个位置采样?要怎样才能实现正确采样呢?这就涉及到了采样点这个概念。

采样点的定义

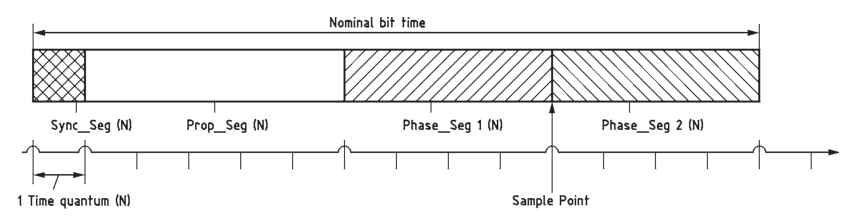

采样点是CAN控制器读取总线电平,并解释各个比特的逻辑值的时间点。在我们了解采样点的测试方法之前,我们需要先了解CAN报文的一个位时间是如何组成的。CAN控制器的最小时间周期称作时间份额(Time quantum,简称Tq),它是通过对芯片晶振周期进行分频而得来的。一个位时间由若干个Tq组成(通常为8到25个),同时根据功能分为4个阶段:同步段、传播段、相位缓冲段1和相位缓冲段2。

这4个阶段的功能如下:

①同步段(Sync_Seg):用于实现时序调整,总线上各个节点的跳变沿产生在同步段内,通常为1个Tq;

②传播段(Prop_Seg):用于补偿网络上的物理延迟时间。这些延迟时间包含信号在总线上的传输延迟和CAN节点内部的处理延迟。传播段保证了2倍的信号在总线上的延迟时间;

相位缓冲段1(Phase_Seg1)和相位缓冲段2(Phase_Seg2):用于补偿跳变沿的相位误差,其长度会在重同步的实现过程中延长或缩短。

采样点位于相位缓冲段1的结尾。由于相位缓冲段1和相位缓冲段2能够延长或缩短,采样点也能够随之变化。

为什么需要测试采样点?

合适的采样点位置是CAN控制器正常通信的保证。

对于CAN网络这个整体而言,各个节点应该尽量使用相同的采样点位置,否则容易出现采样错误,进而使整个网络的通信出现故障;

对于单个节点而言,过早的采样使得节点易受位时间初期的电平波动影响,进而导致采样错误;

受限于重同步的要求和相位缓冲段的宽度,CAN控制器无法过晚采样。

采样点的测试方法

采样点的测试方法:干扰某一位的采样点附近的总线电平,利用CAN错误帧机制,根据ECU是否发送错误帧来判断是否出现采样错误,进而计算ECU的采样点。根据ECU角色的不同,采样点测试的方法可以分为两类:以ECU作为发送节点,干扰它发送的报文;以ECU作为接收节点,干扰它接收的报文。

实际测试环境的总线干扰设备采用VH6501,并以待测ECU作为接收节点,使用VH6501构建仿真报文,然后从后往前逐次翻转仿真报文数据场的时间份额的电平极性,直到总线上出现错误帧。

①在开始采样点测试之前,我们需要设置VH6501自身的采样点;

②VH6501使用一连串的脉冲电平来构建仿真报文;

③从后往前逐次翻转仿真报文数据场的各个脉冲的电平极性,直到干扰到待测ECU的采样点,使得待测ECU发送错误帧。

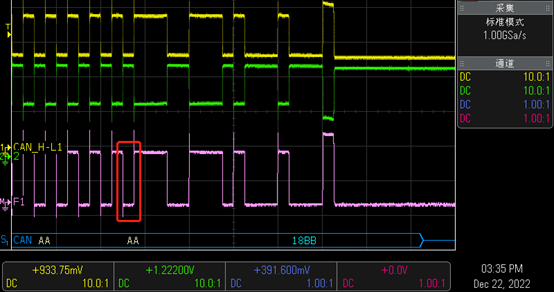

在执行采样点的测试过程中,我们使用示波器截获CAN总线上的波形。样件使用500 Kbps的传统CAN,即位时间为2 μs。示波器时基设置为8 μs,即一个横格可容纳4个位。

上图为没有受到干扰的报文的波形图,图中我们可以清晰地看到数据场的每个比特占用均等的1/4横格。而当我们启动干扰(极性翻转),并且成功翻转采样点所在区间的电平极性后,我们将看到示波器上出现了错误帧,并且数据场最后一个字节的最后一个隐性位相较于正常的波形有着明显的缩短。

采样点测试误差产生的原因

采样点测试误差的来源有测试环境、设备和测试方法等等。

①VH6501和待测ECU之间的位时间偏差造成的系统误差:理想情况下500 Kbps的传统CAN的位时间长度为2 μs,但实际环境里,待测ECU和VH6501的位时间与标准的位时间之间存在一定的偏差。如果ECU的位时间大于VH6501的位时间,采样点的测量结果会比实际值偏大;当样件的位时间小于CANoe设定的位时间,采样点的测量结果会比实际值偏小。这样的系统误差无法通过改进测量方法来降低。

测试方法引起的误差:前文介绍采样点测试方法中提到,采样点测试是通过VH6501翻转待测ECU采样点附近的电平极性实现的。但是采样点是一个“时间点”,而VH6501干扰的是时间段。因此每次干扰的时间段的长度将直接影响采样点测试的误差大小。常用的测试方法中,每个位时间由16个Tq组成,每次翻转一个Tq。最终的实际结果相对于正确结果可能存在±6.25%的偏差。但是在介绍采样点测试方法中我们提到,VH6501使用脉冲序列来构建报文,每个位时间由320个脉冲组成。那么通过缩小每次翻转的电平长度,可以将±6.25%的误差缩减至±0.3125%。

CAN FD采样点测试复杂原因的分析

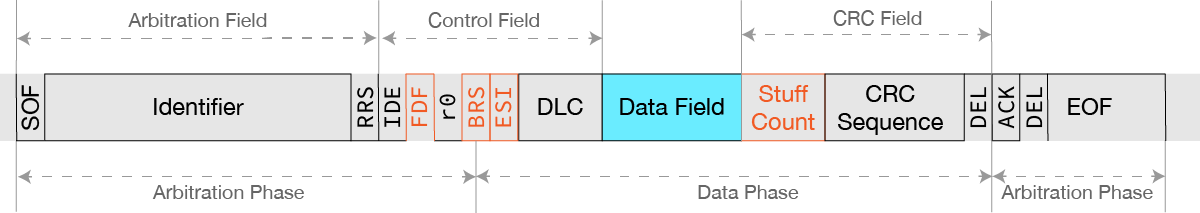

CAN FD报文的结构更复杂且位速率可变。这使得CAN FD采样点测试相较于传统CAN更复杂。CAN FD在位速率较小的仲裁场和位速率较大的数据场分别采用了两个不同的采样点。

CAN FD数据场的位速率视报文的BRS位(Bit rate switch)而调整——当BRS位检测为隐性时,CAN FD的位速率将从仲裁场的最小位速率切换为数据场的数据位速率,这一位速率将持续至CRC界定符的采样点。因此在测量CAN FD采样点时应避免对BRS和CRC界定符进行干扰。同时由于位时间的差异,使用VH6501构造脉冲序列时应考虑到BRS和CRC界定符采样点前后的位速率的切换以及位时间4个阶段的长度变化。

CAN FD的第二采样点

不同于采样点,第二采样点在CAN FD控制器接收其他节点发送报文的过程中并不会起到任何作用。第二采样点的作用,是在不改变传输延迟补偿的情况下,实现CAN FD在数据场的位错误检测要求。

位错误的检测要求发送节点对总线状态进行回读。传统CAN总线在设计之初考虑到了信号在总线上的传播时延以及发送节点TXD和RXD之间的处理时延,这两种时延通过位时间的传播段实现补偿,进而保证了发送节点在发送一个比特期间也能从总线上回读到这个比特。

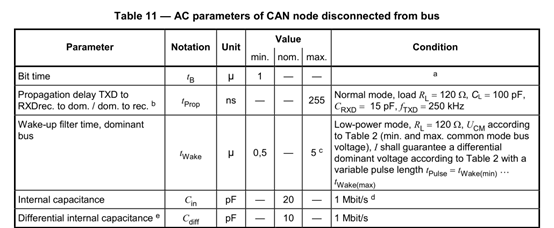

ISO 11898-5规定传输时延的上限为255 ns。位速率为8 Mbps的CAN FD节点的位时间为125 ns。以极限状态下1个位时间由8个Tq组成来计算,单位Tq为15.625 ns。即传输时延需要17个Tq来补偿。显然一个位时间完全不够来补偿传输时延。

解决方法有两种。一是增大位时间,增大传播段的Tq组成数量,但是这种方法会降低位速率,因此和CAN FD高速目标相冲突。二是采用传输时延补偿,即在发送节点回读总线状态时引入一段传输时延补偿,进而保证位错误检测的需要。而引入这段传播时延补偿的结果即为第二采样点(secondary sample point,缩写 SSP)。

SSP对于CAN FD控制器的重要性不言而喻,它是保证控制器在数据段实现位错误检测功能的关键。使用SSP的发送节点会忽略它在采样点检测到的位错误。但是如果在SSP检测到位错误,发送节点将会在下一个采样点对检测到的位错误发出错误帧。

小结

ECU采样点的位置设计是否得当对于通信有着相当大的影响。本文重点介绍了传统CAN采样点的测试方法,并简要分析采样点测试的误差产生原因,同时就CAN FD采样点测试的复杂性和第二采样点进行了介绍。北汇信息专注于汽车电子测试,后续将会为大家带来更多的科普文章,介绍汽车电子及测试相关的知识。同时,也包括本文中所提到的CANFD第二采样点SSP的测试实践经验。

注:图片源自ISO 11898标准以及VC等。